# Embedded Development Platform

# EDP-AM-CO1 Communications Module User Manual

This document contains information on the CO1 communications IO module for the RS EDP system.

### **Contents**

| 1.    | Communications Module EDP-AM-C01                 | 3 |

|-------|--------------------------------------------------|---|

| 1.1   | Controller Area Network Interfaces - CAN         | 3 |

| 1.2   | Serial Interfaces                                | 3 |

| 1.2.1 | RS232 Interfaces                                 | 3 |

| 1.2.2 | RS485                                            | 4 |

| 1.3   | USB Interface                                    | 4 |

| 1.4   | Real Time Clock IC                               | 4 |

| 2.    | User Jumpers And Connectors                      | 4 |

| 2.1   | Mapping Of CPU Pins To The Communications Module | 6 |

| 3.    | Software Support                                 | 7 |

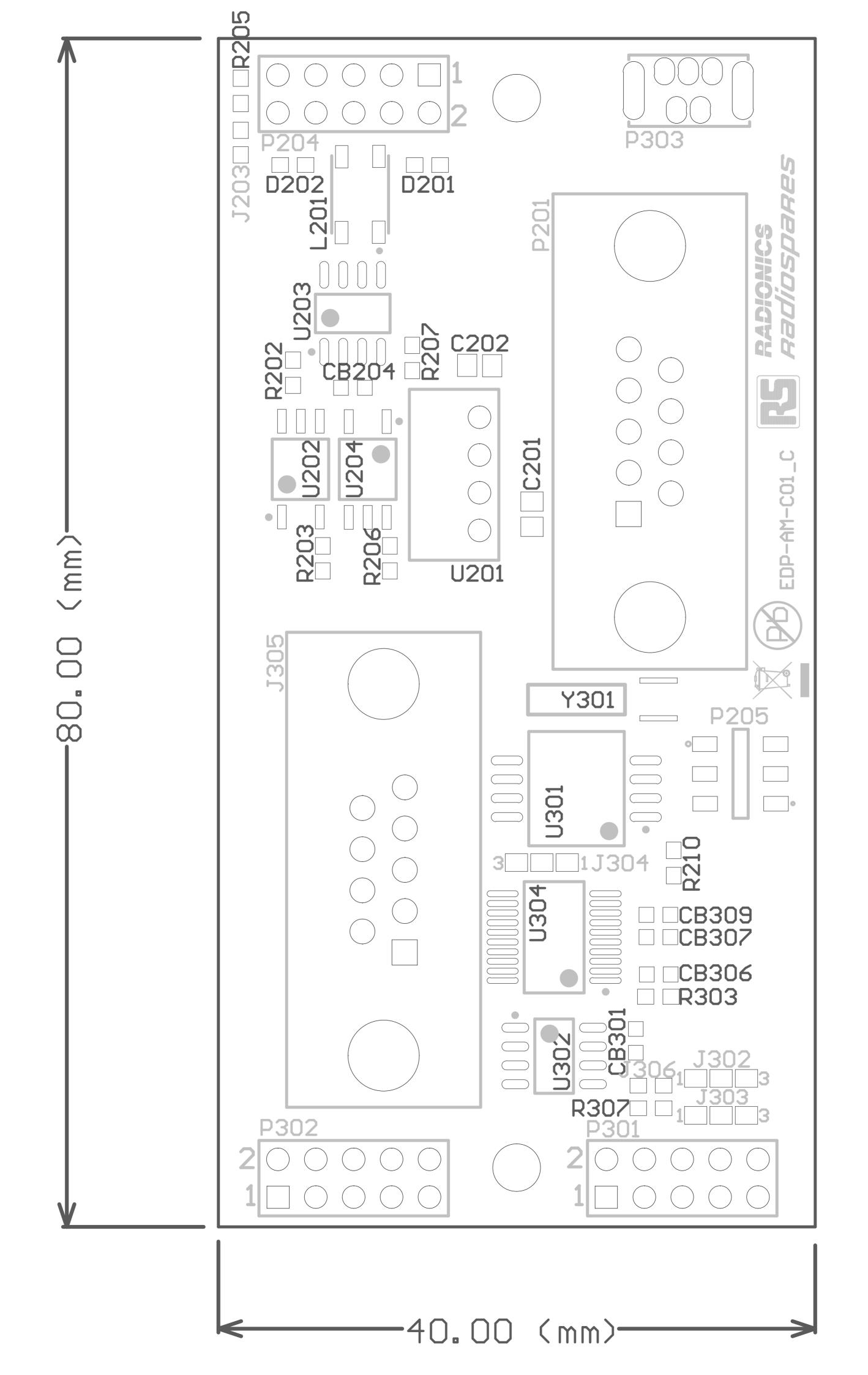

#### 1. Communications Module EDP-AM-C01

This module allows the easy interfacing to the following communication devices present on the CM:

| Comms  |             |            |      |                       |

|--------|-------------|------------|------|-----------------------|

| Туре   | Channel No. | Connector  | Name | Comment               |

| RS232  | ASC0        | 9D Male    | J305 |                       |

|        | ASC0        | 5x2 Header | P302 |                       |

| RS232  | ASC1        | 5x2 Header | P301 | p3 = RX, p5 = TX      |

| RS485  | ASC1        | 5x2 Header | P301 | p3 = RX, p5 = TX      |

| USB    |             | USB mini   |      |                       |

| device | USB DEV     | socket     | P303 | Where available on CM |

| CAN    | CAN CNTRL   | 9D Female  | P201 | 120R on baseboard     |

| CAN    | CAN CNTRL   | 5x2 Header | P204 | Opto-isolated CAN     |

| CAN    | CAN1        | 5x2 Header | P204 | Opto-isolated CAN     |

It also carries a PCF8583 real time clock device on the I2C bus and 240 bytes of non-volatile data storage, powered from the optional lithium battery on the EDP baseboard.

Note: Only one communications module may be fitted to a baseboard at any one time.

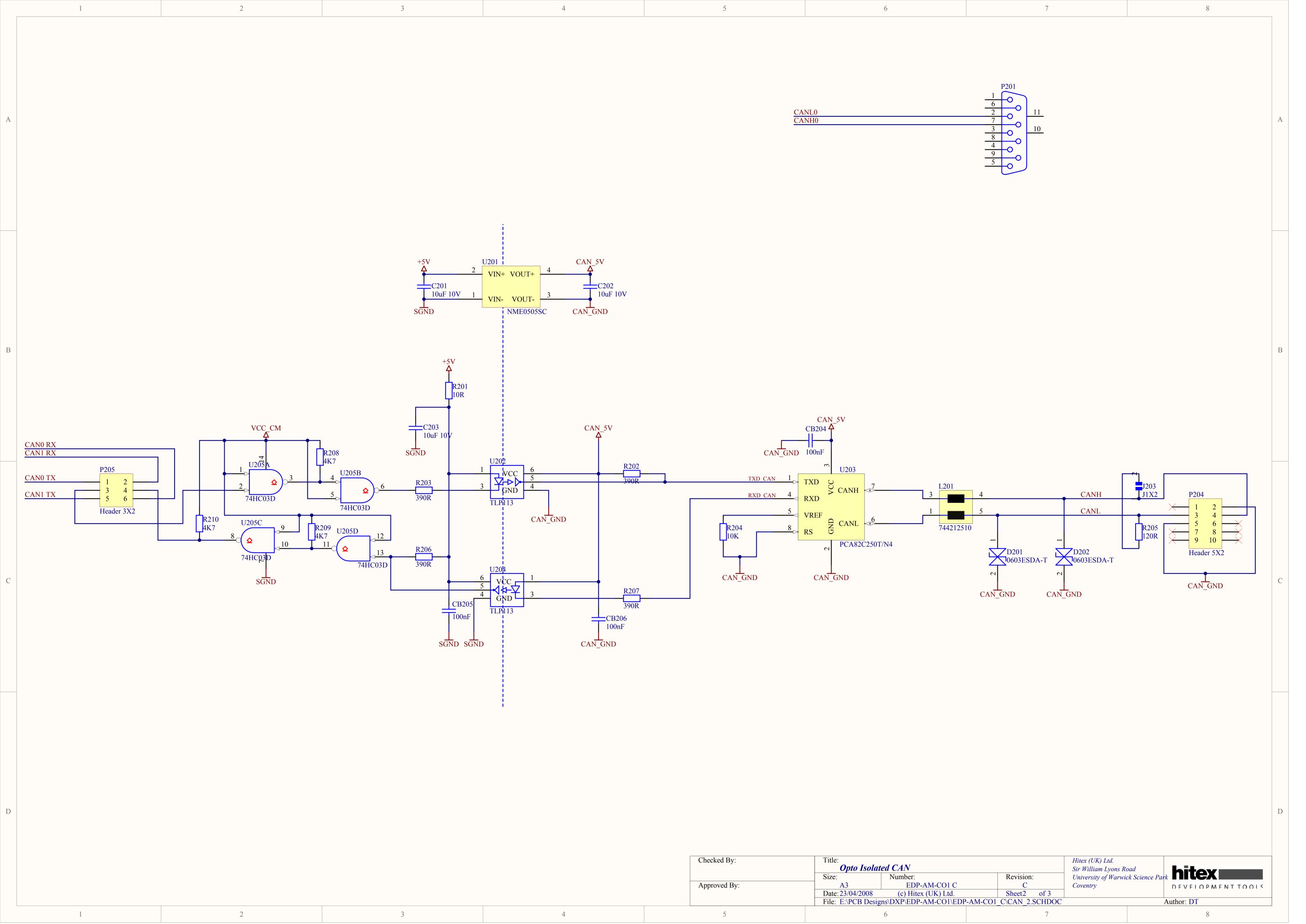

#### 1.1 Controller Area Network Interfaces - CAN

The first CAN channel (CAN0) from the CM (where available) is routed through the 9-D female connector as CAN-High and CAN-Low signals, ready for interfacing to an existing CAN network. CAN0 may also be routed through a galvanically isolated CAN physical layer, emerging on P204 and selectable via P205. If this is required, CAN0 TX and RX connections to the CPU on the CM must be isolated via jumpers on the CM itself (please refer to the user manual for the CM fitted). The isolated physical layer has its own 5V DC-DC convertor so that the EDP system can float relative to other CAN devices.

If the CM has a second CAN channel (CAN1), this can also be routed through the galvanically isolated CAN physical layer via P205.

An optional 120R CAN terminating resistor can be added via solder bridge J203.

#### 1.2 Serial Interfaces

#### 1.2.1 RS232 Interfaces

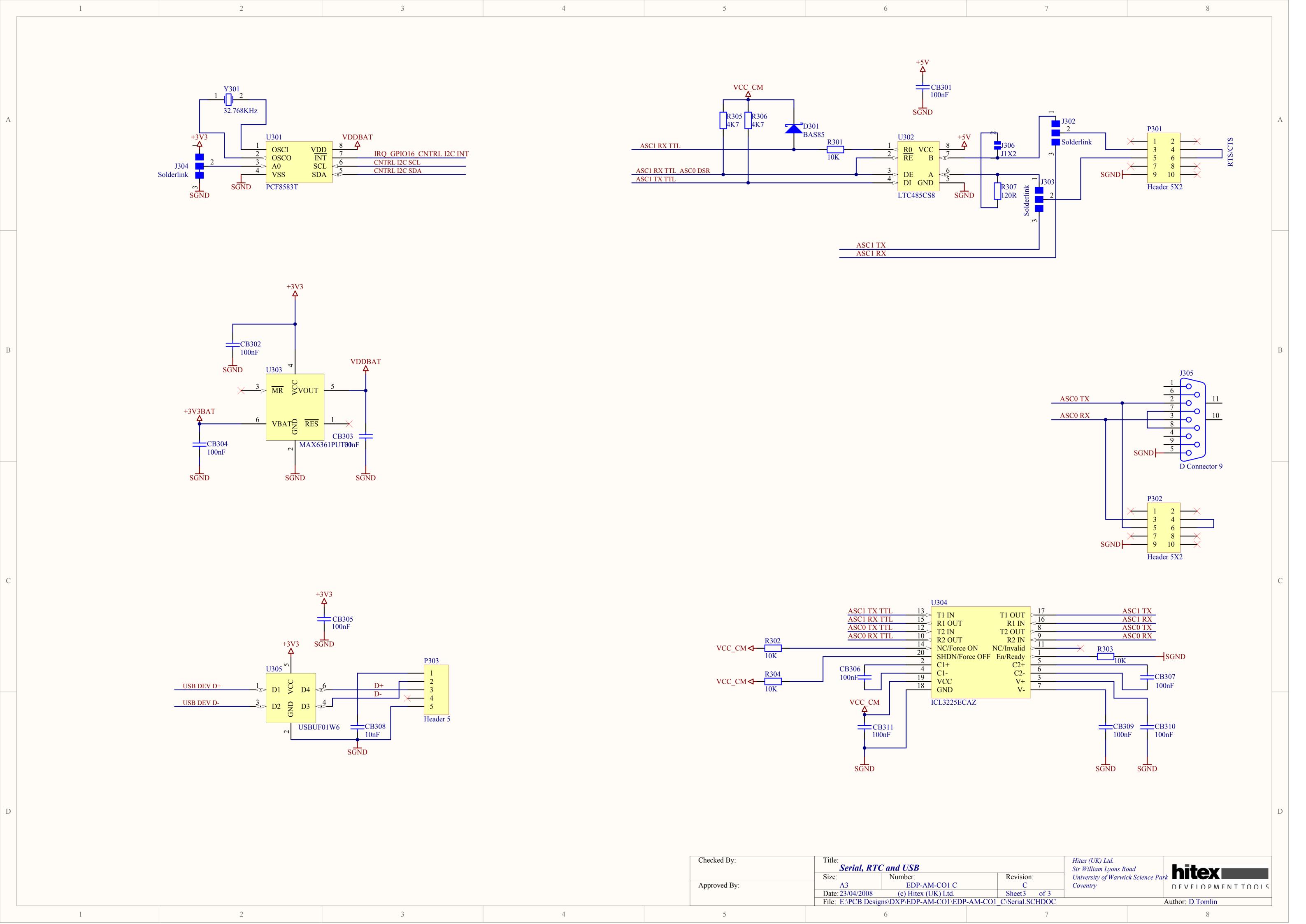

Asynchronous serial channel 0 from the CPU appears as RS232-level signals on the J305 9-D connector. To allow the RS232 connector be mounted away from the EDP hardware, the same signals are available on P302. A simple PC-style IDC 9D connector on a ribbon cable can be used.

For CMs that have a second asynchronous port, it can be routed to P301 where a PC-style IDC 9-D with ribbon cable can be used. Alternatively it can be connected to an RS485 transceiver via jumpers J302 and J303.

#### 1.2.2 RS485

RS485 communications are supported using a Linear Technology LTC485. To make use of this option, the CM software must operate the Receive Enable/Data Enable control line. In RS485 installations where no load resistor is present, J306 allows a default one to be made available.

#### 1.3 USB Interface

The AM unit provides support for USB 'Device' class only and does not provide any support for 'Host' class. The AM board provides a physical layer transient surge arrestor designed specifically to work with high speeds found in USB communication. The USB interface works with those CMs that have a USB peripheral on board that has been mapped to the RS-EDP backplane USB bus signals.

#### 1.4 Real Time Clock IC

The AM module is fitted with an I2C based Real Time Calendar Clock IC. The device has an on board 32KHx watch crystal that maintains real time clock information. The device can be battery backed up via a battery fitted to the Base Board. Interfacing to this device is done via the CNTRL\_I2C signals. All of the CMs currently designed are able to communicate to this device with this interface.

A set of software drivers is provided for each of the CM to allow easy access to this device. A driver library provides software support for setting up sand configuring the RTC clock, as well as displaying the information etc.

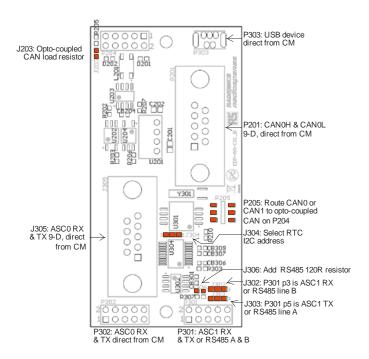

## 2. User Jumpers And Connectors

User-configurable jumpers

#### P205 - Isolated CAN traffic selector

| P205 1-3 | CANOTX TTL traffic is routed to the isolated CAN transceiver   |

|----------|----------------------------------------------------------------|

| P205 3-5 | CAN1TX TTL traffic is routed to the isolated CAN transceiver   |

| P205 4-6 | CANORX TTL traffic is routed from the isolated CAN transceiver |

| P205 2-4 | CAN1RX TTL traffic is routed from the isolated CAN transceiver |

#### J302 & J303 Jumper Options – ASC1 - RS232/RS485 Selector

| J302 2-3 | ASC1 output is RS232 Rx Signal |

|----------|--------------------------------|

| J302 1-2 | ASC1 output is RS485 B Signal  |

| J303 2-3 | ASC1 output isRS232 Tx Signal  |

| J303 1-2 | ASC1 output is RS485 A Signal  |

#### J304 - Real Time Clock Address Select

| J304 1-2 | A0 I2C Slave Address line is set high          |

|----------|------------------------------------------------|

| J304 2-3 | A0 I2C Slave Address line is set low (Default) |

Changing the RTC salve I2C address may be required if there are other I2C devices in the system that shares the same I2C address. Refer to the data sheet for the PCF8583T for the I2C address settings.

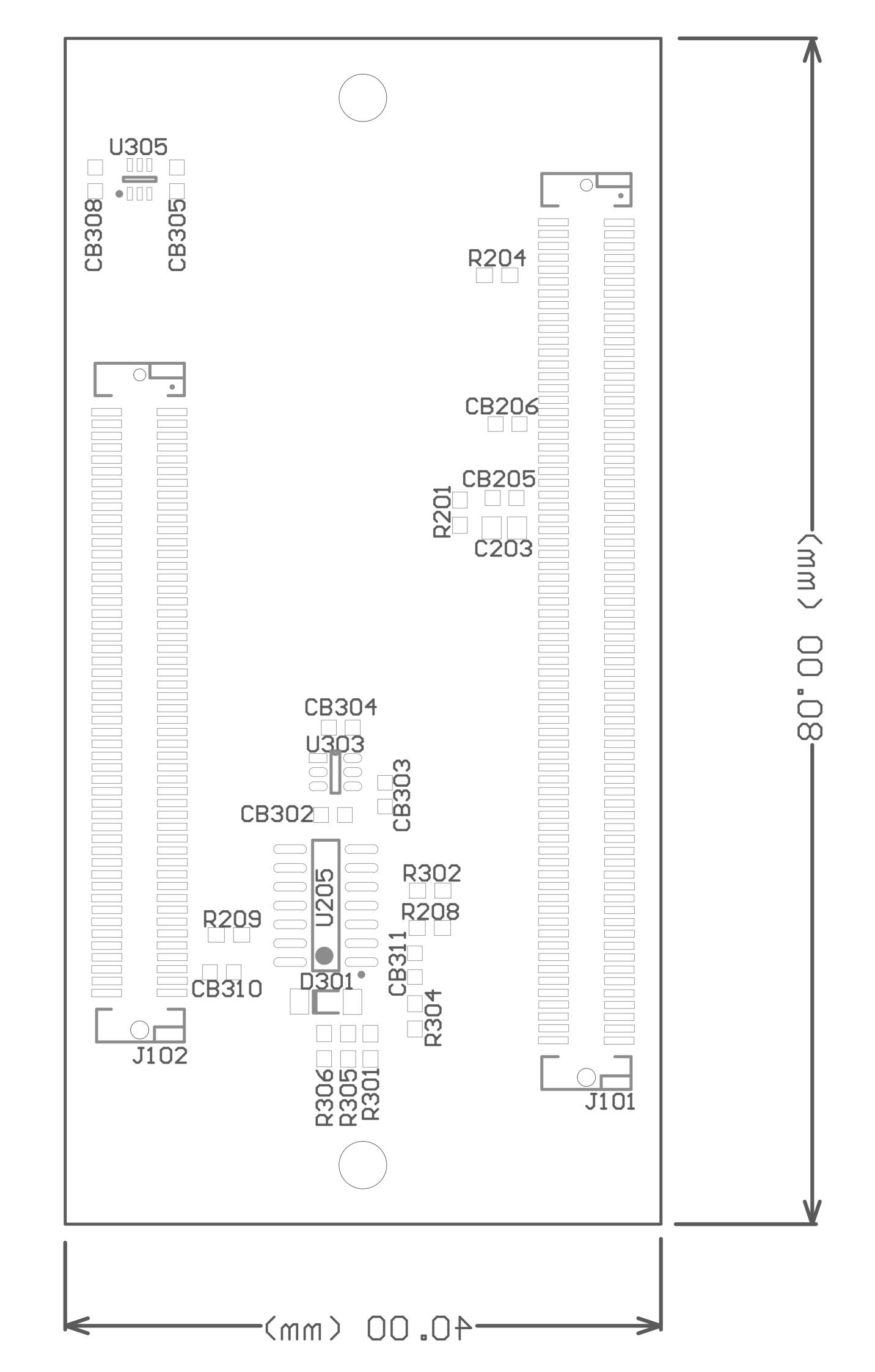

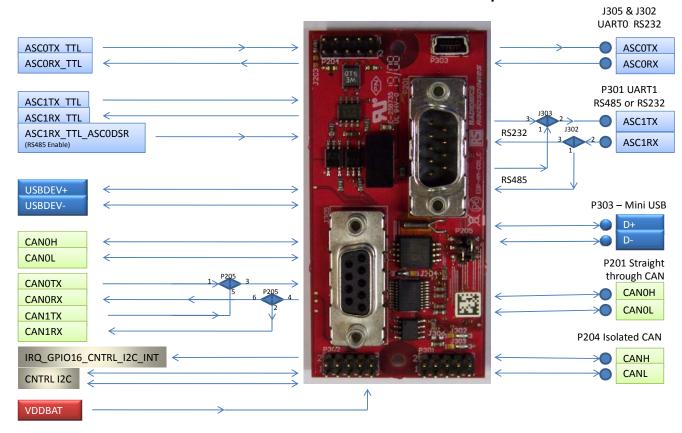

#### **CO1 - Communications Module to RS-EDP Backplane**

Mapping of the Communications module to the backplane

The TTL levels for ASC0 are converted in to RS232 levels by the level shifter on the CO1 AM. The output of this serial channel is on the 9 way D connector.

The ASC1 TTL levels can be converted to either RS232 levels or RS485 levels by selecting the appropriate jumpers. To use RS485 successfully an additional third control signal is required. This is

because RS485 is half duplex and hence it cannot transit whilst receiving. To control the flow a third signal is required which is bought in from the backplane called ASC1RX\_TTL\_ASC0DSR. Not all of the CPU Modules provide support for this signal, so please check with the CM to see if this signal is made available. The output of this serial ASC1 channel is available on the P301 connector. The user should connect a D connector to this, wired for RS232 or RS485 appropriately. Note: RS485 and RS232 have different pinning arrangement on the 9 way D connector, so check on-line for the correct pin out for this.

The USB Device signals USBDEV+ and USBDEV- from the backplane pass through a transient suppressor before exiting the RS-EDP system via a min USB connector P303.

Most of the CPU modules that support CAN have a local CAN transceiver on board, and hence provide the option to supply either the TTL levels CAN0TX & CAN0RX or the physical layer signals CANH and CANL. The CANH & CANL physical layer signals are routed directly onto the 9 way D connector on the Communications Module. For normal operation the user would use the local CAN transceiver on the CM and then route the physical layer CANH and CANL signals down the backplane. The physical layer CAN traffic is then accessed via the 9 way D connector on the Communication Module.

If the user would like isolated CAN traffic then the user would normally set up the Command CPU Module to output TTL level CAN traffic, CAN0TX and CAN0RX instead. This TTL level traffic is then routed via jumper on the Communications Module to a physical layer device which is electrically isolated from the RS-EDP system. This floating CAN output is available on the P204 connector which the user can then attach a 9 way D connector in the normal fashion to access the traffic.

In situations where the main CPU module has two CAN channels then the first CAN channel CAN0 is set up for use with the local CAN transceiver on the CM. This will provide the CAN0H and CAN0L physical layer signals that will appear on the 9 way D connector on the Communications Modules.

The second channel will be set up to output TTL level traffic on CAN1Rx and CAN1TX. This traffic is then routed via the backplane to the Communications module where it is then selected via jumper to enter the isolation circuit and physical layer CAN transceiver. CAN1 isolated physical layer traffic is therefore available on P204.

The AM also has on board a Real time clock device which is supported during power down by a battery on the Base Board. The RTC can be accessed via the CNTRL\_I2C I2C bus. The AM also provides an interrupt line to the MCU to provide wake up etc from RTC alarm events etc.

# 2.1 Mapping Of CPU Pins To The Communications Module

The connectors on the Communications Module are connected to the CPU module as shown below. Only two examples are shown, one for the STR9 module and one for the XC167 module.

Please note that the USB device connector is inactive when the XC167 module is fitted and that that the second serial port is not available when the Ethernet PHY is enabled on the STR9 module.

Finally, there is no second CAN channel available with the STR9 as the MCU does not have a second CAN peripheral. Each of the CMs are different in capability and hence not all of the resource on the AMs is available to all CMs.

| XC167 Pin Allocation | STR9 Pin Allocation           | EDP-AM-CO1 Allocation         |

|----------------------|-------------------------------|-------------------------------|

| Vcc to BB            | Vcc 3V3 or 5V, supplied by CM | Vcc 3V3 or 5V, supplied by CM |

|                      |                               |                               |

| P3.2                 | P5.6                          | IRQ_GPIO16_CNTRL I2C INT      |

| Digital GND          | Digital GND                   | Digital GND                   |

|                      |                               |                               |

| 86 CANOTX            | NC                            | CAN1 TX                       |

|                      |                               |                               |

| 85 CANO RX           | NC                            | CAN1 RX                       |

| 60 RxD1              | P1.1 (PHY Disabled)           | ASC1 TX TTL                   |

| P20.2                | P3.1                          | ASC1 RX TTL_ASC0 DSR          |

| 59 TxD1              | P1.0 (PHY Disabled)           | ASC1 RX TTL                   |

| 69 TxD0              | P5.0                          | ASC0 TX TTL                   |

| 70 RxD0              | P5.1                          | ASCO RX TTL                   |

| Vcc 5V from reg      | 5V from baseboard regulator   | 5V from baseboard regulator   |

|                      |                               |                               |

| Vcc 3V3 from reg     | 3V3 from baseboard regulator  | 3V3 from baseboard regulator  |

|                      |                               |                               |

| XC167 Pin Allocation          | STR9 Pin Allocation                       | EDP-AM-CO1 Allocation                     |

|-------------------------------|-------------------------------------------|-------------------------------------------|

| Vcc to BB                     | Vcc 3V3 or 5V, supplied by CM             | Vcc 3V3 or 5V, supplied by CM             |

| Digital GND                   | Digital GND                               | Digital GND                               |

| Vcc 5V from reg               | 5V from baseboard regulator               | 5V from baseboard regulator               |

| 3V3 Vbatt<br>Vcc 3V3 from reg | 3V3 Vbatt<br>3V3 from baseboard regulator | 3V3 Vbatt<br>3V3 from baseboard regulator |

| XC167 Pin Allocation           | STR9 Pin Allocation            | EDP-AM-CO1 Allocation          |

|--------------------------------|--------------------------------|--------------------------------|

| Vcc 5V from reg                | Vcc 5V from reg                | Vcc 5V from reg                |

| Vcc 3V3 or 5V, supplied by CPU | Vcc 3V3 or 5V, supplied by CPU | Vcc 3V3 or 5V, supplied by CPU |

| Vcc 3V3 from reg               | Vcc 3V3 from reg               | Vcc 3V3 from reg               |

| NC                             | USBDN                          | USB DEV D+                     |

| NC                             | USBDP                          | USB DEV D-                     |

| Digital GND                    | Digital GND                    | Digital GND                    |

| 25 SDA2                        | P2.1                           | CNTRL I2C SDA                  |

| 26 SCL2                        | P2.0                           | CNTRL I2C SCL                  |

| CANLO CANLO                    | CANL0                          | CANLO                          |

| CANHO                          | CANH0                          | CANH0                          |

| 87 CAN1 TX                     | P3.2                           | CAN0 TX                        |

| 84 CAN1 RX                     | P3.3                           | CANO RX                        |

# 3. Software Support

The Communication Module is supported with the appropriate driver software for the respective CM. As there are several CPU Modules each with its own CPU type there exists many versions of the software to exercise the Communication Module. The software provides a supported library for CAN where appropriate, the Real Time Clock set up and configuration, and the UART drivers. Support for the USB is not currently.

Module Position 1

EDPCON1 IO Connector

AN REF AN ANO

AN2

AN4

AN6

AN8

AN10 AN1 AN3 AN5 AN7 AN9 AN11 AN12 AN14 AN13 AN15 GPIO1 VAGND VAGND GPIO0 GPIO2\_MCIDAT0 GPIO3 GPIO5\_I2STX\_WS GPIO4\_MCIDAT1 GPIO6 MCIDAT2 GPIO7\_I2SRX\_CLK GPIO8 MCIDAT3 GPIO9\_I2SRX\_WS GPIO10 MCICLK GPIO11 I2SRX SDA GPIO12\_MCICMD GPIO13 I2STX CLK GPIO14 MCIPWR GPIO15 I2STX SDA IRQ GPIO16 CNTRL I2C INT CPU DACO0\_GPIO17 IRQ GPIO18 I2C GEN0 INT CPU DACO1 GPIO19 IRQ GPIO20 I2C GEN1 INT EVM0 GPIO21 IRQ GPIO22 I2C INT EVM1 GPIO23 GPIO24 AD7 GPIO25 AD15 GPIO26\_AD6 GPIO27 AD14 GPIO28 AD5 GPIO29 AD13 GPIO31 AD12 GPIO30 AD4 GPIO32\_AD3 GPIO33 AD11 GPIO34 AD2 GPIO35 AD10 GPIO36 AD1 GPIO37 AD9 GPIO38\_AD0 GPIO39 AD8 EVG0 GPIO40 EVM2 GPIO41 CAPADC EVG1\_GPIO42 EVM3 GPIO43 EVG2\_GPIO44 EVM4 GPIO45 EVG3\_GPIO46 EVM5\_GPIO47 EVG4\_GPIO48 EVM6 GPIO49 EVG5\_GPIO50 EVM7\_GPIO51 EVG6\_GPIO52 EVM8 GPIO53 EVG7 GPIO54 EVM9 GPIO55 EVG8 GPIO56 EVG9\_GPIO57 EVG10 GPIO58 EVG11 GPIO59 EVG12 GPIO60 EVG13 GPIO61 EVG14 GPIO62 EVG15 GPIO63 EVG16 GPIO64 EVG17 GPIO65 EVG18\_GPIO66 EVG19 GPIO67 ASC0 RX TTL EVM10 GPIO68 ASC0 CTS ASC0 TX TTL EVG20 GPIO69 ASC0 RTS ASC1 RX TTL SPI SSC MRST MISO ASC1 TX TTL SPI SSC MTSR MOSI ASC1 TX TTL ASC0 DTR SPI\_SSC CLK ASC1 RX TTL ASC0 DSR MOTOR P0L SPI SSC #CS NSS MOTOR P0H ETH TX+ MOTOR P1L ETH TX-MOTOR P1H 105 ETH RX+ MOTOR P2L ETH RX-**MOTOR P2H** 109 **MOTOR PWM** ETH LNK LED ETH RX LED **EMG TRP** 113 ETH SPD LED MOTOR H0 ENC0 115 I2C GEN1 SDA MOTOR H1 ENC1 I2C GEN1 SCL MOTOR H2 ENC2 CAN1 RX MOTOR TCO FB CAN1 TX **→**+3V3BAT 123 VCC\_CM**←** 125 → VCC\_CM +3V3**←** +3V3 **->**+5V SGND SGND +12V**✓** +12V +12V**← →**+12V 135 12VGND 12VGND 12VGND 12VGND Tyco Amp 140 Way

# EDPCON2 Bus/Control Connector

|             | #RESIN #RESOUT I2C GEN0 SDA | $\frac{1}{3}$ | 2    | #RESIN<br>#RESOUT                     |

|-------------|-----------------------------|---------------|------|---------------------------------------|

| Ξ           | I2C GEN0 SDA                | 3             | 1    |                                       |

| SGND        |                             |               | 4    | I2C GEN0 SDA                          |

| SGND        | I2C GEN0 SCL                | 5             | 6    | I2C GENO SCL                          |

| SGND —      | IZC GENU SCL                | 7             | 8    |                                       |

| _           | A15 AD15                    | 9             | 10   | A15 AD15 SGN                          |

|             | A14 AD14                    | 11            | 12   | A13_AD13<br>A14_AD14                  |

|             | A13 AD13                    | 13            | 14   | A13 AD13                              |

| _           | A12 AD12                    | 15            | 16   | A12 AD12                              |

| _           | A11 AD11                    | 17            | 18   | A12 AD12<br>A11 AD11                  |

| _           | A10 AD10                    | 19            | 20   | A10 AD10                              |

| _           | A9 AD9                      | 21            | 22   | A10_AD10<br>A9_AD9                    |

| _           | _                           | 23            | 24   |                                       |

| _           | A8_AD8                      | 25            | 26   | A8 AD8                                |

| _           | A7_AD7                      | 27            | 28   | A7 AD7                                |

| _           | A6_AD6                      | 29            | 30   | A6_AD6                                |

| _           | A5_AD5                      | 31            | 32   | A5_AD5                                |

| _           | A4_AD4                      | 33            | 34   | A4 AD4                                |

| _           | A3_AD3                      | 35            | 36   | A3_AD3                                |

| _           | A2 AD2                      | 37            | 38   | A2 AD2                                |

| _           | A1_AD1                      | 39            | 40   | A1_AD1                                |

| _           | A0_AD0                      | 41            | 42   | A0_AD0                                |

| _           | ALE                         | 43            | 44   | ALE                                   |

| _           | #RD                         | 45            | 46   | #RD                                   |

| _           | #WR                         | 47            | 48   | #WR                                   |

|             | #WRH                        | 49            | 50   | #WRH                                  |

|             | #PSEN                       | 51            | 52   | #PSEN                                 |

|             | #CS0                        | 53            | 54   | #CS0                                  |

|             | #CS1                        |               |      | #CS1                                  |

|             | #CS2                        | 55 57         | 56   | #CS2                                  |

|             | #CS3                        | 59            | 60   | #CS3                                  |

|             | CAN0 RX                     |               |      | CAN0 RX                               |

|             | CAN0 TX                     | 61            | 62   | CAN0 TX                               |

|             | USB DEBUG D+                | 63            | 64   | USB DEBUG D+                          |

|             | USB DEBUG D-                | 65            | 66   | USB DEBUG D-                          |

|             | CNTRL SPI CLK               | 67            | 68   | CNTRL SPI CLK                         |

|             | CNTRL SPI MRST              | 69            | 70   | CNTRL SPI MRST                        |

|             | CNTRL SPI MTSR              | 71            | 72   | CNTRL SPI MTSR                        |

|             | CNTRL SPI #CS NSS           | 73            | 74   | CNTRL SPI #CS NSS                     |

| _           | CNTRL I2C SDA               | 75            | 76   | CNTRL I2C SDA                         |

|             | CNTRL I2C SCL               | 77            | 78   | CNTRL I2C SCL                         |

|             | USB HOST D+                 | 79            | 80   | USB HOST D+                           |

|             | USB HOST D-                 | 81            | 82   | USB HOST D-                           |

|             | USB DEV D+                  | 83            | 84   | USB DEV D+                            |

|             | USB DEV D-                  | 85            | 86   | USB DEV D-                            |

| _           | CANH0                       | 87            | 88   | CANH0                                 |

| _           | CANLO                       | 89            | 90   | CANLO                                 |

| _           | CAINLU                      | 91            | 92   | CANLU                                 |

| CC_CM       | <b>√</b>                    | 93            | 94   | ───────────────────────────────────── |

| +3V3        | <                           | 95            | 96   | +3V3                                  |

| +5V         | 4                           | 97            | 98 — | <u></u> +5V                           |

| <b>SGND</b> |                             | 99            | 100  | SGND                                  |

Checked By: Hitex (UK) Ltd. EDP Connectors Number: Revision: Size: EDP-AM-CO1 C Approved By: A3 Coventry (c) Hitex (UK) Ltd. Date: 23/04/2008 Sheet 1 of 3 File: E:\PCB Designs\DXP\EDP-AM-CO1\EDP-AM-CO1\_C\Module Connectors 1.SchDoc

hitex Sir William Lyons Road University of Warwick Science F DEVELOPMENTTOOLS

5

Author: A.Davison